verilog硬件描述语言,从入门到精通

时间:2024-09-29 来源:网络 人气:

深入浅出Verilog硬件描述语言:从入门到精通

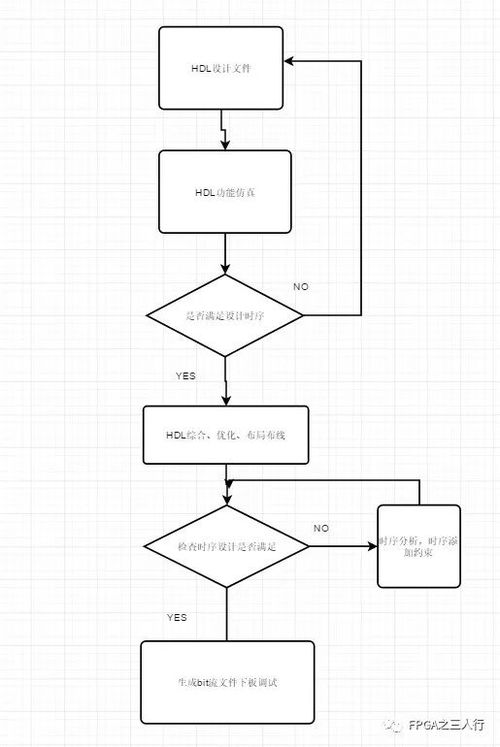

在数字电路设计领域,硬件描述语言(HDL)是工程师们不可或缺的工具。Verilog HDL作为一种广泛使用的硬件描述语言,因其简洁的语法和强大的功能而受到工程师的青睐。本文将为您详细介绍Verilog HDL的基本概念、语法结构、设计方法和仿真技巧,帮助您从入门到精通。

一、Verilog HDL简介

Verilog HDL,全称为Verilog Hardware Description Language,是一种用于描述数字系统硬件结构和行为的文本语言。它被广泛应用于数字电子系统的描述、仿真和综合,以及FPGA(现场可编程门阵列)和ASIC(应用特定集成电路)的开发中。

二、Verilog HDL的基本语法

Verilog HDL的语法类似于C语言,但也有一些本质的区别。以下是一些基本的语法元素:

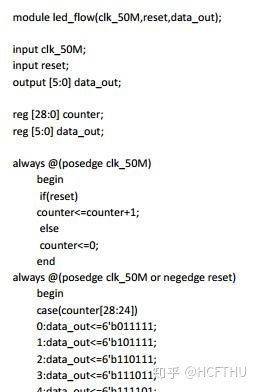

模块(Module):Verilog HDL中的基本单元,用于定义电路的功能和结构。

端口(Port):模块的输入和输出接口,用于与其他模块进行交互。

数据类型:Verilog HDL支持多种数据类型,如整数、实数、逻辑等。

连续赋值语句(Continuous Assignment):用于描述电路的输出与输入之间的关系。

过程块(Procedural Block):用于描述电路的行为,如always块和initial块。

三、Verilog HDL的设计方法

Verilog HDL的设计方法主要包括以下几种:

行为级设计:描述电路的功能和行为,不涉及具体的硬件实现。

结构级设计:描述电路的组成和结构,包括模块的连接和层次结构。

门级设计:描述电路的硬件实现,包括逻辑门、触发器等。

四、Verilog HDL的仿真技巧

仿真是在设计过程中验证电路功能的重要手段。以下是一些Verilog HDL的仿真技巧:

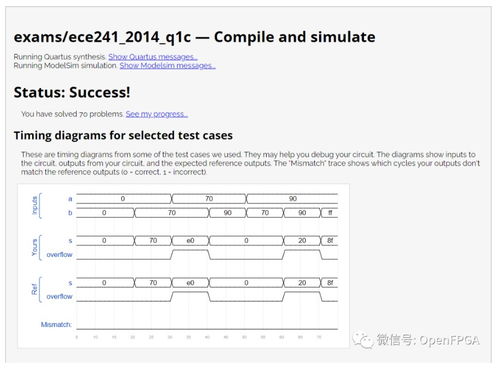

测试平台(Testbench):用于生成输入信号,观察电路的输出响应。

波形图(Waveform):用于显示电路的时序波形,分析电路的性能。

断点(Breakpoint):用于在仿真过程中暂停执行,观察电路的状态。

五、Verilog HDL的高级特性

Verilog HDL具有许多高级特性,以下是一些常见的特性:

任务(Tasks):用于执行非阻塞操作,如延时、条件判断等。

函数(Functions):用于执行计算和逻辑操作,提高代码的可读性和可维护性。

多维数组:用于存储和操作多维数据,如矩阵、向量等。

结构体:用于组织复杂的数据结构,提高代码的复用性。

系统函数:用于访问硬件资源,如时钟、复位等。

六、Verilog HDL的编码风格与最佳实践

良好的编码风格和最佳实践对于提高代码的可读性和可维护性至关重要。以下是一些Verilog HDL的编码风格和最佳实践:

命名规范:使用有意义的变量和模块名称,提高代码的可读性。

模块化设计:将功能相关的代码组织成模块,提高代码的复用性。

注释:添加必要的注释,解释代码的功能和实现细节。

Verilog HDL是一种功能强大、应用广泛的硬件描述语言。通过本文的介绍,相信您已经对Verilog HDL有了初步的了解。在实际应用中,不断学习和实践,才能不断提高自己的Verilog HDL技能。

相关推荐

教程资讯

教程资讯排行